Elsyca

Capitalizing on knowledge and expertise in electrochemistry to deliver unique comprehensive multiphysics digital twin solutions.

Guarantee assets integrity, gain reduction in operational costs, increase production capacity, and get early visibility on products quality.

Protect

Leverage innovative digital twin solutions to protect entire assets from corrosion

- ability to accurately predict the variety of factors responsible for corrosion;

- gathering, correlation, and empowerment of field data to guide strategic decisions;

- support of the development of protection systems that comply with industry norms and standards;

- empower interoperability in-between teams and partners.

Pipeline Networks

Avoid business disruption by implementing the most effective corrosion-prevention strategies for your entire network.

Storage Tanks

Holistic and non-intrusive assessment of corrosion risks to develop effective risk based inspection and avoid costly repairs.

Offshore Wind Farms

Prevent external and internal corrosion of wind turbines structures.

Offshore Oil & Gas

Prevent corrosion of offshore platforms, retrofit with efficient cathodic protection systems, and extend platforms service life.

Infrastructures

Avoid expensive repair operations.

Pipeline Networks

Avoid business disruption by implementing the most effective corrosion-prevention strategies for your entire network.

Storage Tanks

Holistic and non-intrusive assessment of corrosion risks to develop effective risk based inspection and avoid costly repairs.

Offshore Wind Farms

Prevent external and internal corrosion of wind turbines structures.

Offshore Oil & Gas

Prevent corrosion of offshore platforms, retrofit with efficient cathodic protection systems, and extend platforms service life.

Infrastructures

Avoid expensive repair operations.

Plate

Unlock the full potential of your surface finishing and plating operations via digital twin solutions

- encapsulate your company expertise and gain agility for future applications;

- verify and guarantee upfront the design for manufacturing and quality of all your products;

- uplift your production capacity while maintaining quality and industry standards;

- reduce trials iterations, material waste, post-processing, and manpower operations;

Functional Plating

Establish efficient plating operations and more durable products.

Decorative Plating

Ensure the appealing aspects of your products with optimum costs

PCB Plating

Ensuring PCBs quality throughout the full cycle, from design to production.

Electrocoating

Verify upfront the resulting paint layer thickness distribution over entire BIW model

Electropolishing

Control the quality of metal removal for smoother surfaces

Anodizing

Ensure even growth of the metal oxide layer

Functional Plating

Establish efficient plating operations and more durable products.

Decorative Plating

Ensure the appealing aspects of your products with optimum costs

PCB Plating

Ensuring PCBs quality throughout the full cycle, from design to production.

Electrocoating

Verify upfront the resulting paint layer thickness distribution over entire BIW model

Electropolishing

Control the quality of metal removal for smoother surfaces

Anodizing

Ensure even growth of the metal oxide layer

Corrosion Modeling

Predict corrosion apparition to increase the lifecycle of your components.

Acoustics

Improve acoustic interior comfort.

Meshing

Automate your meshing operations for high quality surface and volume meshes.

Research & Development

Learn more about our continuous investments in new technologies.

Corrosion Modeling

Predict corrosion apparition to increase the lifecycle of your components.

Acoustics

Improve acoustic interior comfort.

Meshing

Automate your meshing operations for high quality surface and volume meshes.

Research & Development

Learn more about our continuous investments in new technologies.

How do we deliver?

Our pillars

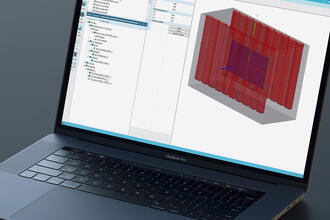

Software

Elsyca's expertise is translated into a software portfolio helping various industries to protect their assets, optimize their plating processes, innovate, and ensure final product quality.

Services

Elsyca's services offering covers consultancy projects, dedicated training, software support, and laboratory material characterization to ensure that whatever the chosen solution, our users get the most out of it.

Technology Transfer

Elsyca's goal is to ensure that every solution is the most appropriately deployed on the user's side. Every investment in Elsyca's solutions comes with a tailored deployment program to maximize the benefits of our solutions.

Research & Development

Since its origins and continuing until today, Elsyca invests in research and development to leverage its unique electrochemical knowledge through software simulation tools and technology transfer.

Our recent content

Discover moreTrusted by 400+ companies worldwide

Willing to learn more about our solutions?

Get in touch with our team of experts